# ヒステリシス制御方式単インダクタ2出力 スイッチング電源の研究

小堀 康功\*1, 小林 春夫\*2

Single Inductor Dual Output Switching Converter with Hysteretic Control

# Yasunori KOBORI and Haruo KOBAYASHI

This paper proposes a new SIDO (Single Inductor Dual Output) DC-DC switching converter with hysteretic control. It requires few additional components (a comparator and a latch) to control two DC-DC converters with single inductor, buck and buck converters or boost and boost converters.. We investigated exclusive control method which converts only one converter except another converter for some clock periods. The architecture of exclusive control method is to compare two errors of the output voltage and to decide the converter that is controlled next time. This control method has the merit not to depend on either output voltage or output current. We describe circuit topologies, operation principles and simulation results.

KEYWORDS: DC-DC converter, SIDO converter, Switching converter, Hysteretic control

# 1. INTRODUCTION

DC-DC converters are indispensable for virtually all electronic devices, from cell phones to large manufacturing machinery. In many applications, multiple output voltages are required. In a conventional system, the DC-DC converter needs a single inductor for each output, hence many inductors are needed in the system as a whole. In order to reduce cost and volume of the system, it is desirable to reduce the number of required inductors. Single inductor multi output (SIMO) converters have been recently reported, especially dual output (SIDO) converters [1]-[3]. In this paper, we propose a new control method for SIMO converters which requires few additional components (a switch, a diode and a comparator), while not requiring a saw tooth generator nor current sensors. We introduce their operating principles and show simulation results to verify their basic operation and performance of SIDO converters and show the experimental results of SIDO converter.

# 2. SISO HYSTERETIC CONVERTER

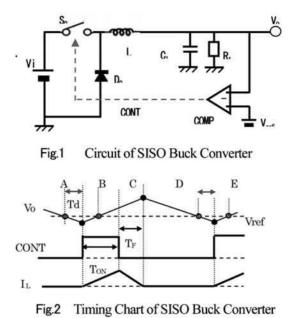

2.1 SISO Buck Converter with Hysteretic control Fig. 1 shows a single inductor single output (SISO)

\*1 電気電子創造工学科(Dept. of Innovative Electrical and Electronic Engineering) E-mail: kobori@oyama-ct.ac.jp

<sup>\*2</sup> 群馬大学理工学部(Division of Electronics and Informatics, Gunma University)

buck converter with hysteretic control and Fig.2 shows the timing chart. In Fig. 1, the output voltage Vo is compared at the comparator with the reference voltage Vref. In Fig. 2, when Vo goes down less than Vref, the output signal CONT from the comparator turns HI with a slight delay Td at time B. The main switch So is controlled ON when the CONT signal from the comparator turns HI.

While So conducts, source energy is supplied to the capacitor C1 and the load resistor R1 through the inductor L. When Vo goes higher than Vref at time C, the CONT signal is turned LO and So turns OFF with a slight delay at time D as shown in Fig. 2. Between the time B and C, the rising current of the inductor  $I_{LR}(t)$  is expressed in (1).

$$I_{LR}(t) = (V_i - V_0) \cdot t / L$$

(1)

The top value of the current  $I_D$  at D is expressed in (2) using the period  $T_{ON}$ .

$$I_D = I_{LR}(T_{ON}) = (V_i - V_0) T_{ON} / L$$

(2)

After So turns OFF, the current of the inductor  $I_L$  in the buck converter maintains the energy stored on C1 through the diode Do. At this time, the current  $I_L(t)$ continues to flow and Vo is over charged shown in Fig.2. The falling current  $I_{LF}(t)$  is expressed in (3) and the period  $T_F$  from D to E is solved as (5) and (6). The value of L is usually about 1uH in order to make this over charge small. Thereafter the inductor current goes to zero and Vo goes down.

$$I_{LF}(t) = I_D - Vo \cdot t / L$$

(3)

$$I_{LF}(T_F) = (Vi - Vo) T_{ON} / L - Vo \cdot T_F / L = 0$$

(4)

$$\therefore \quad T_F = \{(V_i - V_0)/V_0\} \cdot T_{ON} \quad (5)$$

$$=$$

(Vi / Vo - 1) T<sub>ON</sub> (6)

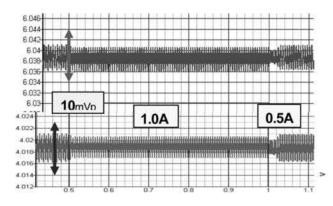

Fig. 3 shows simulation results of dynamic regulation when the output current Io is changed between 1.0 and 0.5 A, and Table 1 shows the parameters of Fig. 1. The input voltage Vi is 9V and the output voltage Vo is 5V and the output current is changed. The ripple of the output voltage Vo is 7 mVpp at Io=1.0 A and 2 mVpp at Io=0.5 A. The dynamic load regulation is less than 6 mVop, measured by the overshoot when Io is changed.

Table 1. Simulation Parameters of Buck Converter

| Vie | 9.0 V+     |  |

|-----|------------|--|

| Lo  | 1.0 µH.    |  |

| Co  | 470 μF.    |  |

| Voe | 5.0 V.     |  |

| Io₽ | 1.0∕0.5 A∘ |  |

Fig. 3 Simulation Results of Buck Converter

## 2.2 SISO Boost Converter with Hysteretic control

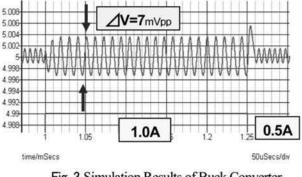

Fig. 4 shows the SISO boost converter with hysteretic control and Fig. 5 shows the timing chart. In Fig. 4, the clock pulse needs to drive the inductor ON/OFF when the output signal PWM of the comparator is always HI. When the main switch So is ON, the inductor charges energy by storing current. Then So is OFF, the energy in the inductor is supplied to the capacitor and the load resistor through the diode Do. As a result, the capacitor is charged and Vo goes up as in Fig. 5.

Fig. 6 shows the simulation result when the output current is changed between 1.0 and 0.5 A. The output voltage ripple is 7mVpp at Io=1.0A and at 0.5A and there is no overshoot. There appears a slight DC offset of 2mV. In this case, the clock pulse is asynchronous to the PWM signal because the boost converter is not controlled by any periodic signal. The clock pulse is only used to start the boost converter, and has a frequency of 500 kHz and a duty cycle of about 90%.

# 3. SIDO HYSTERETIC CONVERTER

3.1 SIDO Buck Converter and Simulation Results

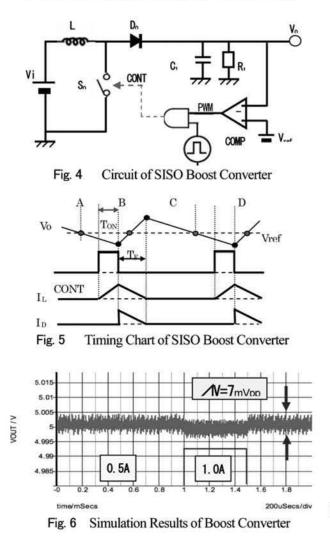

The proposed SIDO converter with hysteretic

control is shown in Fig. 7, where the circuit in the red dotted line is a high side converter and the circuit in the blue line is a low side converter. In this case, the high side output voltage  $V_H$  is higher than the low side voltage  $V_L$ . In Fig. 7, the output  $V_H$  or  $V_L$  is connected with the OP amplifier OP<sub>H</sub> or OP<sub>L</sub> to be compared with each reference voltage  $V_{TH}$  or  $V_{TL}$ . Their outputs  $\Delta V_H$  and  $\Delta V_L$  are connected with OR gate and inputs of the comparator COMP (red triangle). When the output voltage is lower than Vr, the error voltage  $\Delta V$  which is the output of OP-amp is higher (logically HI). Then the output of OR gate is HI and the main switch So is controlled ON. Then current through the inductor is supplied to the high side converter or the low side one.

Both error voltages  $\Delta V_H$  and  $\Delta V_L$  are HI, switch S2 decides which converter to be controlled or to be supplied energy. When S2 is ON, the low side converter is selected to be controlled. In this case, the anode of the diode D1 is about  $V_L$  and D1 is OFF because of  $V_H > V_L$ . S2 is controlled by the signal SEL which is the output of the comparator connected with two  $\Delta V$  signals. The converter whose error voltage  $\Delta V$  is larger is always supplied energy in preference to the other.

When  $V_H$  and  $V_L$  are both higher than Vr, neither converter needs energy. In this case, the output of OR gate is LO and CONT signal is LO, then switch So turns OFF and no energy is supplied to either converter. Fig. 8 shows the simulation results when the output current I1 is changed between 1.0 and 0.5 A and I2=0.5 A. Table 2 shows the parameters of the circuit in Fig. 7. In Fig. 8, the output voltage ripples are about 5 mVpp at I1=1.0 or 0.5A. Here, self regulation is the load

regulation for current change of itself and cross regulation is the load regulation for current change of another converter. In this case, they are almost zero, hence the regulation is very good. In this simulation, there is a slight DC offset; 38mV at V1=6V and 19mV at V2=4V.

| Vie               | 9.0 V+     |

|-------------------|------------|

| Lع                | 0.5 µ H₽   |

| C٠                | 470 μF.    |

| V <sub>H</sub> o  | 6.0 Ve     |

| VL <sup>o</sup> ? | 4.0 V.     |

| I1+               | 1.0/0.5 A. |

| I2ø               | 0.5 A.     |

Table 2 Simulation Parameters of Buck Converter

Fig. 8 Simulation Result of Buck Converter

## 3.2 SIDO Boost Converter and Simulation Results

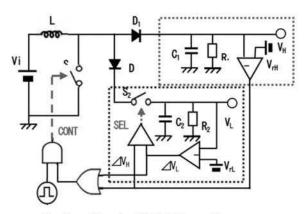

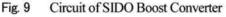

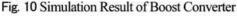

Fig. 9 shows the SIDO boost converter with hysteretic control. In this circuit, the main switch So is driven by the output of an AND gate, whose inputs are a clock pulse and the output of an OR gate. The OR gate has two inputs like the SIDO buck converter. Table 3 shows simulation parameters of Fig. 9.

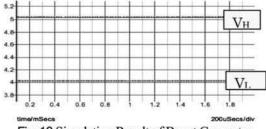

Fig. 10 and Fig. 11 show simulation results of the SIDO boost converter. Output voltages are controlled correctly and their voltage ripples are about 6 mVpp when output current of the high side converter is changed between I1=1.0 and 0.5 A. There is a slight DC offset of about 2 mV.

Table 3 Simulation Parameters of SIDO Boost Converter

| Vie              | 3.0 V.   | - |

|------------------|----------|---|

| La               | 1.0 µH₽  |   |

| Co               | 470 µ F. |   |

| V <sub>H</sub> o | 5.0 V.   |   |

| VLo              | 4.0 V¢   |   |

| Fck.             | 500 kHz. | _ |

Fig. 11 Output ripples of Boost Converter

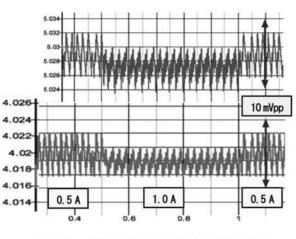

## 4. SIMO BUCK CONVERTER (4 Outputs)

#### 4.1 Circuit and Operation of SIMO Converter

The proposed SIMO converter with four outputs is shown in Fig. 12. The circuit shown in the red dotted line is the sub-converter that is a plug-in type circuit. Here, the switch S in the sub-converter is individually controlled by the output of the self-comparator. In this schematic, the relation of the output voltages is usually V1 >V2 >V3 >V4. When the plural switches are ON at the same time, the sub-converter of the lowest voltage has priority over other sub-converters to be supplied current from the inductor. In the case that there is no need to supply any energy, all switches are OFF then the inductor current flows through the diode Dr to recharge the source battery Vi. In this circuit, there is a clock pulse in order to control the main switch So smoothly and to limit the response frequency under the clock frequency.

Fig. 12 SIMO Buck Converter (4 Outputs)

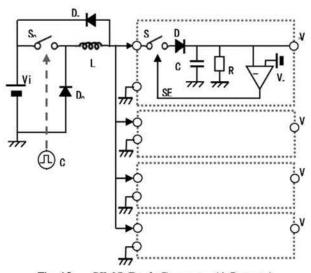

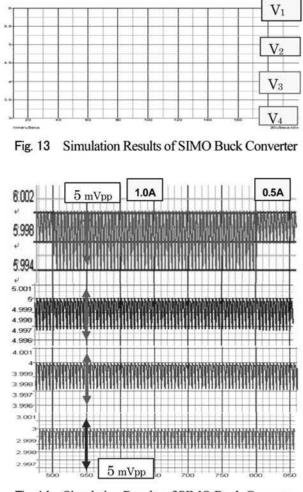

## 4.2 Simulation Results of SIMO buck converter

Fig. 13 and Fig. 14 show the simulation results and Table 4 shows the simulation parameters of the SIMO converter. In Fig. 13, the output voltages are 6.0V, 5.0V, 4.0V and 3.0V respectively. In Fig. 14, output currents of  $12\sim14$  are 0.5 A and current of sub-converter 1 is changed from 0.5A to 1.0A and vice versa.

The output ripples of SIMO converter are about 3 mVpp at 11=0.5 A. The ripple of sub-converter 1 becomes large about 6 mVpp at I1=1.0 A. This large ripple occurs because sub-converter 1 is controlled last after other converters are controlled. Sub-converter 1 has to wait for the longest time against other sub-converters. Self regulation and cross regulations are very good because of little overshoot shown in Fig. 14.

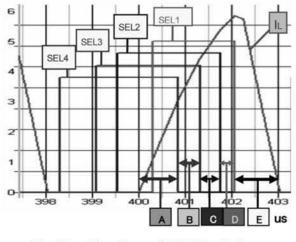

Fig. 15 shows the SEL signals in each sub-converter at II=0.5A when current flows through inductor  $I_L$ . The voltage level of SEL signal in each sub-converter is shown to be different from other one in order to easily check its operation. Many SEL signals are ON at the same time, though in reality, the highest priority SEL signal is selected to be supplied energy at any one time. For example, SEL4 is selected in area A, SEL3 in area B and SEL1 in area D. In area E, all switches are OFF, but inductor current flows through the diode Dr.

Fig. 14 Simulation Results of SIMO Buck Converter

Vie

9.0 Ve

Le

1.0  $\mu$  He

Ce

500  $\mu$  Fe

Voe

6/5/4/3 Ve

I1e

1.0/0.5 Ae

I2~I4e

0.5 Ae

Eck(D)e

200 kHz (D=0.5)e

Fig. 15 Wave Form of SIMO Buck Converter

# 5. EXPERIMENTAL RESULT OF CONVERTER

## 5.1 Experimental Result of SISO Buck Converter

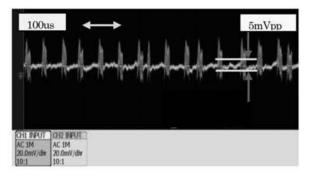

Fig. 16 shows the experimental output ripple of single output (SISO) converter with hysteretic control. The conditions are Vi=9V, Vo=4V, Io=0.35A, L=1uH and C=470uF. The voltage ripple is less than 5 mVpp except switching noise. There is some switching noise and instability noise because the circuit is made on a universal board, so there appears high frequency noise caused by parasitic impedance in the ground pattern.

## 5.2 Experimental Results of SIDO Buck Converter

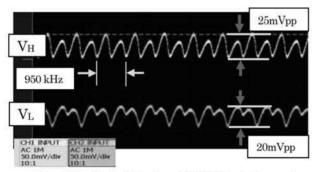

Fig. 17 and Fig.18 show the experimental output ripples of SIDO converter with hysteretic control and Table 5 shows the experimental parameters of this converter. In Fig. 17, the output current of the high side

Fig. 16 Experimental Results of SISO Buck Converter

converter  $I_H$  is 0.35 A and the output current of the low side converter  $I_L$  is 0.20 A. In this case, the high side ripple  $V_H$  is 25 mVpp and the low side ripple  $V_L$  is 20 mVpp. The frequency of the switch controlled signal (CONT signal shown in Fig. 7) is about 950 kHz.

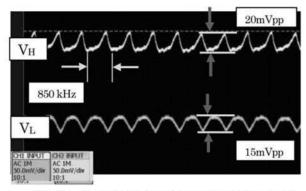

In Fig. 18, the high side ripple  $V_H$  is 20 mVpp and the low side ripple  $V_L$  is 15 mVpp when the output currents are  $I_H$ =0.50 A and  $I_L$ =0.20 A. The frequency of the CONT signal is about 850 kHz. In this case, the output current is larger than Fig.16, the ripples are less and the frequency is lower than Fig. 17.

Fig. 17 Output Ripples of SIDO Buck Converter (I<sub>H</sub>=0.35 A, I<sub>L</sub>=0.20 A)

Fig. 18 Output Ripples of SIDO Buck Converter (I<sub>H</sub>=0.50 A, I<sub>L</sub>=0.20 A)

Table 4 Simulation Parameters of SIMO Converter

| Vie              | 6.0 V.   |  |

|------------------|----------|--|

| Lu               | 1.0 µ H₂ |  |

| Co               | 470 μFe  |  |

| V <sub>H</sub> P | 4.0 V.   |  |

| V <sub>L</sub> . | 3.0 V.   |  |

| I <sub>H</sub> P | 0.35 A₊  |  |

| Ι <sub>L</sub> ρ | 0.20 A₊  |  |

| SW.              | P-MOS₽   |  |

Table 5 Experimental Parameters of SIDO

## 6 Load Regulations of SIDO Buck Converter

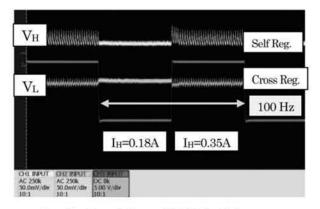

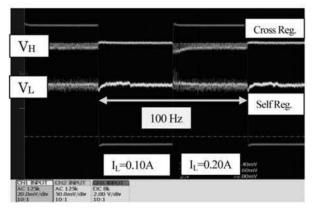

Fig. 19 shows the self regulation of high side output  $V_H$  and the cross regulation of low side output  $V_L$  of SIDO buck converter. In Fig. 19, high side output current  $I_H$  is changed from 0.18A to 0.35A and vice versa. The overshoot of  $V_H$  or  $V_L$  is little enough. In Fig. 20, low side output current  $I_L$  is changed 0.10 / 0.20A. The overshoots of both are less than 10 mVop.

Fig. 19 Regulations of SIDO Buck Converter  $(I_H=0.35 / 0.18 \text{ A}, I_L=0.10 \text{ A})$

Fig. 20 Regulations of SIDO Buck Converter  $(I_H=0.18 \text{ A}, I_L=0.20 / 0.10 \text{ A})$

# 7. CONCLUSION

In this paper, we have described several kinds of single inductor dual/multi output (SIDO/SIMO) converter with hysteretic control. We have investigated and proposed new control methods for SIDO/SIMO converters, which are independent of output voltage and current. We have proposed SIDO/SIMO buck converters and SIDO boost converter, and have explained their principles of operation and verified their basic operation by simulations. Also we have shown experimental results for these SISO/SIDO buck converters.

In experimental results of SIDO buck converter, output voltage ripples are from 15 mVpp to 25mVpp at  $I_H=0.5$  / 0.35 A and  $I_L=0.20$  A. Dynamic load regulations like self regulation or cross regulation are less than 10 mVop when the high side current is changed  $I_H=0.35$  / 0.18 A, and almost 0 mVop when the low side current is changed  $I_L=0.20$  / 0.10 A

## REFERENCES

- H. Iwase, T. Okada, T. Nagashima, T. Takagi, Y. Kobori, et. al. "Realization of Low-Power Control Method for SIDO DC-DC Converter," in IEEJ Technical Meeting of Electronic Circuits, ECT-12-037, Yokohama, Japan (Mar. 2011)

- Y.Kobori, M.Li, H.Kobayashi, et al. "Single Inductor Dual Output DC-DC Converter Design with Exclusive Control," IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Kaohsiung, Taiwan (Dec. 2012)

- 3) Y.Kobori, F. Zhao, Q. Li, S. Wu, H.Kobayashi, et al. "Single Inductor Dual Output Switching Converter using Exclusive Control Method," IEEE Power Engineering, Energy and electrical Devices (POWERENG), Istanbul, Turkey (May. 2013)

【受理年月日 2013年 9月30日】