# A Study on Analog Circuit Fault Detection Using Supply Current Test

### Satoshi NISHINO

Oyama National College of Technology 771 Nakakuki Oyama-shi, Tochigi 322 Japan

> Tel. +(81) 285 25 3630, Ext.348 Fax. +(81) 285 21 0359

### ABSTRACT

By making a discrete circuit model of a typical Op Amp  $\mu$ A741 's internal circuit, the IC-Op Amp's fault modes was investigated. The above experiment's result is that, the Op Amp's internal transistor fault was represented by the supply current's abnormal value.

The fault detection experiment was performed on 3 analog boards using IC-Op Amps. A fault detection rate of approximately 90% was obtained.

The results of this research, verified the usefulness of the supply current test to detect faults in analog circuits.

#### 1. Introduction

Fault detection and diagnosis methods in digital circuits have long been established.

These methods have been applied to many kinds of circuits. However, the same could not be said in the analog circuit case due to the variety of circuits available.

Analog circuit fault detection and diagnosis methods have been discussed recently by [1], [2] and [3]. In this paper, a standard IC used in analog circuits, the Op Amp in its fault mode will be discussed.

Circuit simulation is usually used to analyze the circuit in the fault mode, however, in this paper, a discrete circuit will be used instead.

When a discrete Op Amp is implemented, the transistor size, the line width and length of the internal circuit connection, as well as the delay time would be different from the actual IC-Op Amp. However, since this paper will only discuss surge fault detection, these differences would not matter.

This paper assumes that defects such as internal circuit connection shorts or transistor faults does not occur in the manufacturing process. Moreover surge faults only occur in the user's side. In the surge fault mode, damage is done to the oxide film insulation and to the p-n junction. Moreover, there is melting in the internal aluminum circuit.

On the user's side, the following could be considered the causes that results to defective ICs: intrusion of static electricity, a miss operation resulting in high voltage supplied to the chip, surge voltage generated by the on and off switching of other equipment.

In this paper, the surge experiment was performed in six steps to simulate the fault that occurred in the IC-Op Amp.

Most recently, almost all analog circuits have been implemented using IC-Op Amps. Thus, in this paper, three analog circuits was constructed on the PCB. In the above surge experiment, a defective IC-Op Amp was used and the supply current experiment was performed on the board level.

### 2. The IC-Op AmP

#### 2.1 IC-Op Amp Fault Discussion

In 1968, the  $\mu$ A741 was initially introduced and the  $\mu$ A709 later followed as an improvement. Because of its reliability, the  $\mu$ A741 is an Op Amp for general use.

This circuit consists of three big blocks.

The first block consists of transistors  $Q_1$  to  $Q_8$  which is the differential amplifier. The second block consists of  $Q_{17}$  and  $Q_{18}$  which is the Darlington pair. The third block consists of  $Q_{14}$  and  $Q_{20}$  which is the push-pull amplifier.

Thus, the output of the  $\mu$ A741 depends on which block one or more defective transistor occurs.

Also, the output depends on whether this defective transistor is in the stuck at ON fault or stuck at OFF fault condition.

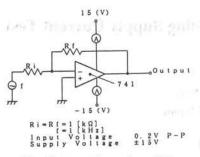

In order to discuss these IC-Op Amp fault conditions, the  $\mu$ A741 Op Amp and its discrete equivalent is both configured as an inverting

Fig.1 Inverting Amplifier

amplifier (Fig. 1). Steps 1) and 2) is first applied to the  $\mu$ A741 Op Amp as mentioned in the procedure below, then steps 3) to 6) is applied to the discrete fault model, then the circuit supply current and output of both models are measured.

Experimental procedure:

IC-Op Amp:

- 1) Supply a high voltage to each IC-Op Amp terminal to destroy the IC.

- 2) On another IC, leave each IC pin unconnected one at a time to simulate an open condition.

#### 2.1.1 IC-Op Amp Fault Experiment

The following nine fault experiments are performed to simulate an IC-Op Amp that is destroyed, in many cases, by a surge current att he user's side.

A: Apply a ± 35V at the power supply terminal.

B: Apply a ± 45V at the power supply terminal.

C: Apply a ± 55V at the power supply terminal.

D: Apply an inverse ± 15V at the power supply terminal.

E: Apply ± 50 V between pins 2 and 5.

| F:  | Apply | $\pm$ | 50 | V | between | pins | 7 | and | 6. |  |

|-----|-------|-------|----|---|---------|------|---|-----|----|--|

| G:  | Apply | $\pm$ | 50 | V | between | pins | 3 | and | 6. |  |

| H:  | Apply | ±     | 50 | V | between | pins | 6 | and | 4. |  |

| I : | Apply | ±     | 50 | V | between | pins | 3 | and | 1. |  |

|     |       |       |    |   |         |      |   |     |    |  |

Table 1 shows the supply current and output voltage of the nine ICs above in an inverting circuit (0 dB). In this table, when pin 7 (+ voltage terminal) and pin 4 (- voltage terminal) was supplied an overvoltage, the positive (+) and the negative (-) supply current for chips A, B, C, D,F and H resulted in a zero current in either or both cases.

Table 2 mentioned below, shows the case in

Table 1 Inverting Circuit Using Defective IC-Op AmP

| No.       | Supply                                               | Current                                                                                                                               | Output Condition                                                                                                                    |  |  |  |  |  |  |  |  |

|-----------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

|           | l+ [mA]                                              | I- [mA]                                                                                                                               | output condition                                                                                                                    |  |  |  |  |  |  |  |  |

| ABCDEFGH- | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c} -3. & 19 \\ -5. & 12 \\ -3. & 96 \\ -3. & 22 \\ -9. & 87 \\ 0. & 00 \\ -1. & 12 \\ 0. & 00 \\ -4. & 89 \end{array}$ | -8.2V D. C<br>-10.5V D. C<br>-10.4V D. C<br>-8.0V D. C<br>-8.0V D. C<br>Same as Input<br>+14.0V D. C<br>Same us Input<br>-7.2V D. C |  |  |  |  |  |  |  |  |

# Table 2 The Case of Each Terminal Open (IC-Op AmP)

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Supply                                                                                                                                                                                                                                         | Current                                                                                                                                                        | Output Condition                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Pin No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | [+ [mA]                                                                                                                                                                                                                                        | [-[m∧]                                                                                                                                                         | output condition                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

| 2<br>3<br>4<br>6<br>7<br>&& 4<br>6<br>7<br>&& 4<br>6<br>7<br>2<br>&& 4<br>6<br>7<br>2<br>2<br>&& 4<br>6<br>7<br>4<br>6<br>7<br>3<br>3<br>&& 6<br>7<br>4<br>6<br>7<br>3<br>4<br>6<br>7<br>8<br>4<br>6<br>7<br>8<br>8<br>4<br>6<br>7<br>8<br>4<br>6<br>7<br>8<br>8<br>4<br>6<br>7<br>8<br>8<br>4<br>6<br>7<br>8<br>8<br>4<br>6<br>7<br>8<br>8<br>4<br>6<br>7<br>8<br>8<br>4<br>6<br>7<br>8<br>8<br>8<br>4<br>6<br>7<br>8<br>8<br>8<br>6<br>7<br>8<br>8<br>8<br>6<br>7<br>8<br>8<br>8<br>6<br>7<br>8<br>8<br>8<br>8 | $ \begin{array}{c} 6. & 7 & 0 \\ 1. & 4 & 5 \\ 4. & 0 & 5 \\ 1. & 7 & 1 \\ 0. & 0 & 0 \\ 6. & 6 & 0 \\ 4. & 0 & 6 \\ 1. & 2 & 4 \\ 0. & 0 & 0 \\ 4. & 0 & 6 \\ 2. & 0 & 4 \\ 0. & 0 & 0 \\ 0. & 0 & 0 \\ 0. & 0 & 0 \\ 0 & 0 & 0 \end{array} $ | $\begin{array}{c} -1,19\\ -6,30\\ 0,00\\ -1,71\\ -6,25\\ -1,09\\ 0,00\\ -1,24\\ -6,57\\ 0,00\\ -2,04\\ -5,57\\ 0,00\\ 0,00\\ 0,00\\ 0,00\\ 0,00\\ \end{array}$ | + 1 4. 0 V D. C<br>- 1 2. 2 V D. C<br>- 1. 0 V D. C<br>Same as Input<br>- 1 2. 4 V D. C<br>+ 1 4. 0 V D. C<br>- 1 2. 4 V D. C<br>+ 1 0. 2 V D. C<br>- 1 2. 8 V D. C<br>- 1 2. 8 V D. C<br>Same as Input<br>- 1 2. 8 V D. C<br>Same as Input<br>Same as Input<br>Same as Input |  |  |  |  |  |  |  |  |  |

which each terminal of the IC-Op Amp is open. When pin 7 (+ supply) is made open, the Op Amp will have the same condition (+ supply current is zero) as Op Amp A, B, C and D which was applied an over voltage in the power supply terminal.

When pin 6 (output) and pin 7 (+ supply) is made open, the IC-Op Amp will have the same condition ( $\pm$  supply current is zero) as IC-Op Amp F. The above mentioned case results when the supply terminal is applied an over voltage, melting the internal aluminum connection to the power supply terminal, resulting to a disconnection with the supply voltage and/or also causing damage to the surrounding transistors.

After applying an over voltage to the inputoutput terminal (pin 2,3), and the offset adjust terminal (pin 1, 5), the Op Amp will have the same fault condition as above.

In the IC-Op Amp E, G and I, after an overvoltage was applied to the input-output (pin 2, 3) and offset adjust terminals (pin 1, 5), an abnormal amount of current flowed that damaged the IC-Op Amps internal resistors.

Fig. 2 shows the internal pattern condition of a defective IC-Op Amp C.

### Fig.2 Defective IC's Internal Print Pattern

#### 2.1.2 IC-Op Amp's Individual Terminal Open

In the above mentioned IC-Op Amp's fault detection experiment, melting of the supply voltage terminal occurs when the supply voltage terminal was applied an overvoltage.

To simulate this condition, the individual terminals in Table 2 were opened. Then the supply current and the output was measured.

When pin 4 and 7 of the IC-Op Amps in Table 2 wereopened, with the supply current becoming zero (0), it can be concluded that melting occured in the internal aluminum connection to the supply voltage terminal.

## 2.2 Fault Mode of the IC-Op Amp

From the fault experiment of (1) to (6), the fault occurring in the IC-Op Amp at the user's side can be considered to have the following conditions:

1) The internal aluminum connection to the power supply terminal melts when the supply voltage terminal is applied an overvoltage, disconnecting the voltage supply to the internal circuit.

2) When the input/output terminal or offset adjust terminal is applied an overvoltage, the internal transistors are destroyed, resulting to the decrease and increase of the positive or negative supply current below or beyond its normal value.

Since it is possible for condition 1) and 2)to occur simultaneously, thus in this case, the supply current becomes zero.

Moreover, in the IC-Op Amp fault experiment, with an overvoltage applied to each individual IC-Op Amp terminal, even if all the terminals are applied an overvoltage by a surge current in actual conditions, cases 1) and 2) would occur at the same time thus, the voltage would become zero.

When a fault in the user's side occurs, this can be due to one or more causes. The application

of an overvoltage, the change in the ambient temperature, moisture, or surge voltages generated by the surrounding equipment, influences the IC-Op Amp to be in the fault condition.

Since a computer simulation to duplicate the environment that caused the fault condition at the user's side is not possible, it is necessary to simulate the fault condition by actually constructing the circuit and insert defective IC-Op Amps.

#### 3. Threshold Level and Fault Detection Rate

#### 3.1 Threshold Level

The IC-Op Amp supply current varies according to the ambient temperature and the IC characteristics. Thus, by constructing an inverted IC-Op Amp using Fig. 2, measuring the supply current and varying the temperature range from 10 °C to 40 °C, the supply current, as shown in (1) is a random variable x having a normal distribution with a mean  $\mu$  and a standard deviation  $\sigma$ ,

$$y(x) = \frac{1}{\sqrt{2\pi}\sigma} \exp(-\frac{(x-\mu)^2}{2\sigma^2})$$

(1)

letting x = I, the threshold range is determined to be,

$$\mu - 3 \sigma < I < \mu + 3 \sigma \tag{2}$$

## 3.2 Fault Detection Rate for a Single Defective Transistor (In the discrete Op Amp model) The following are the results for $\mu$ and $\sigma$ ,

| [Positive supply current]: | $\mu + = 2.07  [mA]$     |

|----------------------------|--------------------------|

|                            | $\sigma + = 0.20  [mA]$  |

| [Negative supply current]: | $\mu - = -2.07  [mA]$    |

|                            | $\sigma - = 0.20  [mA].$ |

Thus, in the normal operation, the supply current range is,

1. 4.7 < I < 2.6.7 [mA] (3)

Using the threshold range in equation (3) on the results of the previous open or shorted transistor experiment, the single defective transistor fault experiment which had 60 combinations, resulted in a fault detection rate of 81%.

## 3.3 Fault Detection Rate for Multiple Defective Transistors (In the discrete Op Amp model)

Applying the above mentioned threshold range to Table 6, resulted in the fault detection rate of 79%. This is because 15 out of the 19 fault combinations in the experiment resulted in supply currents falling outside the range.

### 3.4 Supply Current Fault Detection Limitation

Concluding from the above mentioned fault experiment result, the possible output conditions can be sorted as follows:

- (1) Positive DC voltage output

- (2) Negative DC voltage output

- (3) Normal AC output voltage with an offset value

- (4) Normal output voltage with large supply current

- (5) High frequency oscillation (about 10kHz)

- (6) Waveform distortion

- (7) Normal output with normal supply current

It is possible to detect faults having output conditions (1) to (4) using the supply current, but it is not possible with the output conditions (5) to (7). It is possible to detect faults with output conditions (5) and (6), by using an oscilloscope to observe the output waveform. Detecting a fault in output condition (7) is not possible because, the output and supply current is not influenced by the internal fault condition, however, this is a rare case.

#### 4. Supply Current Model of IC-Op AmP

#### 4.1 Non Fault Model

#### \* Case 1

For the case of parallel, series and mixed configuration Op Amps, the total current i, in the PCB can be represented by the following equation,

$i_t = \sum_{i=1}^{n} i_i$  (4)

i : individual IC supply current. \* Case 2

For the case of complex Op Amp circuit configuration, for example passive and / or active devices in the feedback loop, different power supply voltages, etc., the total current in this case becomes,

$$\mathbf{i}_{\mathbf{a}} = \sum_{i=1}^{n} \mathbf{i}_{\mathbf{a}i} \tag{5}$$

i. : each IC's added current

i. : total current in the added circuit. Total current in the PCB becomes,

$$i_{t}' = \sum_{i=1}^{n} i_{i} + \sum_{i=1}^{n} i_{ai}$$

(6)

The general case is,

$$\sum_{i=1}^{n} i_{i} > \sum_{i=1}^{n} i_{ai}$$

(7)

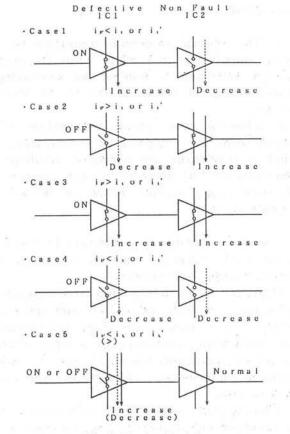

### 4.2 Fault Model

\* Case 1

Shown in Fig. 3 is a defective IC1 that is permanently switched on, resulting in a high supply current value. In this case, IC1's output affected IC2 by reducing the value of the supply current value at IC2. This resulted in a total supply current value less than the total supply current at the non fault condition.

i<sub>F</sub>: Total Supply Current at Fault Condition \* Case 2

In the same figure is a defective IC1 that is permanently switched off, resulting in a low supply current value. In this case, IC1's output affected IC2 by increasing the supply current

Fig.3 Fault Model

-118-

value at IC2. This resulted in a total supply current value higher than at the non fault condition.

\* Case 3

In the same figure is the case where IC1 does not influence IC2. The defective IC1 is switched ON permanently resulting in a high supply current value. The total supply current value in this case is higher than at the non fault condition. \*Case 4

In this case, IC1 does not influence IC2. The defective IC1 is switched OFF permanently, resulting in a low supply current value. The total supply current value in this case is less than at the non fault condition.

\* Case 5

In this case, defective IC1 does not influence non fault IC2.

### 5. Supply Current of Each IC

### 5.1 Supply Current of Non Fault IC-Op Amp

This paper discusses the variation of the supply current due to the influence of the input voltage and frequency.

The following results were observed,

- (1) Inverting Op Amp circuit

- \* The supply current's value increases as the input voltage is increased.

- \* The supply current was not influenced by the variation in the input voltage and frequency.

- (2) Voltage Follower

- \* Varying the input voltage and frequency has no effect on the value of the supply current.

## 5.2 Supply Current of Defective IC-Op Amp

Using 5 defective IC-Op Amps coming from the user side, inserting them into the 2 circuits above and measuring the supply currents, the following were observed,

- (1) Inverting Op Amp circuit

- \* The supply current was not influenced by the variation in the input voltage and frequency.

- (2) Voltage Follower

- \* The supply current was not influenced by the variation in the input voltage and frequency.

All of the above results suggest that the supply current value is not influenced by the variation in the input voltage and frequency. This observation is true except for the inverting Op Amp circuit case in the non fault condition.

### 6. Fault Detection Experiment of Analog Boards

The experiment was performed by constructing three analog boards using  $\mu$  A741 and applying fault conditions Ato I as shown previously in Table 1.

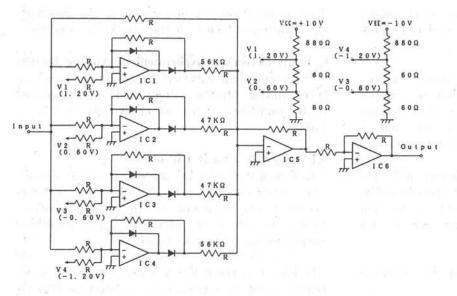

### 6.1 Piecewise Linear Circuit

In Fig. 4 is shown the piecewise lin-ear circuit. The supply current value of this circuit was measured by the change of the ambient temperature. Using this result, the plus and minus threshold range was calculated as follows:

16. 5 < I < 17.7 [mA] (8)

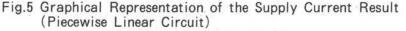

In Fig. 4, if the 6 IC-Op Amps, IC1 to IC6 are replaced one at a time with a defective IC(case A to I in Table 1), a circuit with 54 different fault combinations can be obtained. The supply current results from this experiment can be graphically depicted as shown in Fig. 5.

In Fig. 5, it can be seen that of the 54 different fault combinations, 6 cases (shaded bars) occur wherein both the positive and negative supply currents fell within the threshold range. The resulting fault detection rate was computed to be 88.9%.

However, in this circuit, changing the position of the fault IC does not change the total supply current, thus IC fault diagnosis is not possible. \* Computed versus Measured Values

| $\mu: +, -$    | ·Computed Value 1.71 [mA] $\times$ 6    |

|----------------|-----------------------------------------|

|                | = 10.26 [mA]                            |

|                | • Measured Value 17.10 [mA]             |

| $\sigma: +, -$ | • Computed Value 0.20 $\times \sqrt{6}$ |

|                | = 0.49 [mA]                             |

|                | • Measured Value 0.34 [mA]              |

V1 to V4 (from  $\pm$  10 volts) is app-lied to IC1 to IC4 through resistor R respectively, as shown in Fi-g. 4. Since current will flow fro-m the  $\pm$ 10 volt supply thus, meas-ured current value is larger than the computed value, this falls under the Non Fault Model Case 2.

| <insertion< th=""><th>of Defective I</th><th>C-Op Amp</th><th>G to IC1 Case&gt;</th></insertion<> | of Defective I               | C-Op Amp               | G to IC1 Case>         |

|---------------------------------------------------------------------------------------------------|------------------------------|------------------------|------------------------|

| $\mu$ : +                                                                                         | · Computed                   | Value 1.71             | $\times$ 5 + 6.66 [mA] |

|                                                                                                   |                              | 1 - 1 <sup>4</sup> - 1 | = 15.21 [mA]           |

|                                                                                                   | <ul> <li>Measured</li> </ul> | Value                  | 17.00 [mA]             |

|                                                                                                   | <ul> <li>Computed</li> </ul> | Value 1.71             | $\times$ 5 + 1.12 [mA] |

|                                                                                                   |                              |                        | = 9.67 [mA]            |

|                                                                                                   | <ul> <li>Measured</li> </ul> | Value                  | 16.70 [mA]             |

Fig.4 Piecewise Linear Circuit

In this fault case, the supply current of the defective IC is constant as shown in the filter circuit experiment below (Table 3). Thus, by considering that the supply current of the non fault IC-Op Amp increases by a value of 1.79 [mA], this fault case falls under Fault Model Case 3. In this case, it was not possible to detect the fault.

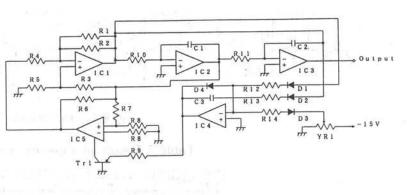

#### 6.2 Sine Wave Oscillator Circuit

Shown in Fig. 6 is the sine wave oscillation circuit. In Fig. 6, if the 4 IC-Op Amps IC1 to IC4 are replaced one at a time with a defective IC(case A to I in Table 1), a circuit with 36 different fault combinations can be obtained. The supply current result in this experiment can be graphically depicted as shown in Fig. 7.

The threshold range in this case was determi-ned to be,

[Positive supply current]: 8.26 < I < 10.3 [mA]

[Negative supply current]: 9.68 < I <11.7 [mA].

In Fig. 7, it can be seen that of the 36 different fault combinations, 2 cases (shaded bars) occur wherein both the positive and negative supply currents fell within the threshold range. The resulting fault detection rate was computed to be 94.4% (34/36).

However, in this circuit, changing the position of the fault IC does not change the total supply current, thus IC fault diagnosis is not possible.

\* Computed versus Measured Values

<Non Fault>

μ: +,- · Computed Value 1.71 × 5 [mA] = 8.55 [mA] + · Measured Value9.28 [mA] - · Measured Value 10.69 [mA]

σ: + · Computed Value 0.20×√5 = 0.45 [mA] · Measured Value0.34 [mA]

$r: - \cdot \text{Computed Value } 0.20 \times \sqrt{5} = 0.45 \text{ [mA]} \cdot \text{Measured Value}$  0.34 [mA]

<Insertion of Defective IC-Op Amp G to IC1 Case>

µ: + ·Computed Value 1.71 × 4 + 6.66 [mA]

= 13.50 [mA]

Measured Value 850 [mA]

Computed Value

1.71 × 4 + 1.12 [mA]

7.96 [mA]

Measured Value 10.20 [mA]

In the (+) case, by inserting a defective IC-Op Amp G, the total supply current was lesser than that in the non fault case. Thus, by considering that the supply current of the non fault IC-Op Amp decreases, this falls under Fault Model Case 1.

In the (-) case, by inserting the same defective IC-Op Amp, the total supply current was largerthan that in the non fault case. Thus, this falls under Fault Model Case 3, by considering that the supply current of the non fault IC-Op Amp increases.

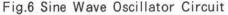

### 6.3 Filter Circuit

### 6.3.1 Supply Current Dependence on Input Voltage and Frequency

Using 4 Op Amps in a filter circuit as shown in Fig. 8, the same experiment as in the previous two circuits was performed. However, in this case, the individual IC supply current was measured. Using this result, the supply current distribution in the fault condition will now be discussed.

In Fig. 8, by varying the input voltage and frequency of the filter circuit and measuring the supply current, it was observed that the supply current did not vary.

## 632Supply Current Dependence on Chip Location

Using the same Fig. 8 and interchanging the 4 ICs, this resulted into 24 different combinations. Measuring the supply current, it was observed that it remained constant, a part is shown in Table 3. Thus, total supply current does not depend on the chip location.

### 6.3.3 Individual IC Supply Current Dependence on Chip Location

Performing the experiment as in 6.3.2 but using (1) or (4) defective ICs, the result is shown in Table 4. From this result, it can be concluded that the individual IC supply current does not depend on the chip location, because, the supply current of the defective IC is constant even in

Fig.7 Graphical Representation of the Supply Current Result(Sine Wave Oscillator Circuit)

different locations. Thus, the use of the total supply current as a parameter to detect faults is possible.

If it is possible to measure each IC's individual supply current, then it would be possible to diagnose the fault IC.

## 6.3.4 Result of Fault Detection, Computed and Measured Value

The threshold of the filter circuit is shown below.

[Positive supply current] : 3.88 < I < 3.98 [mA] [Negative supply current]: 3.72 < I < 4.08 [mA]. By inserting one or two defective IC-Op Amps

Fig.8 Filter Circuit

Table 3 Result of Interchanging 4 ICs

| f (Hz) | Location | 1 - 2 - 3 - 4<br>[mA] | $\begin{array}{c} 4-3-2-1 \\ [ \mathfrak{u} \lambda ] \end{array}$ | 1 - 2 - 4 - 3<br>[mA] | 3 - 2 - 4 - 1<br>[mA] |

|--------|----------|-----------------------|--------------------------------------------------------------------|-----------------------|-----------------------|

| +      | 10       | 3.93                  | 3.92                                                               | 3.92                  | 3.92                  |

|        | 100      | 3.93                  | 3.92                                                               | 3.92                  | 3.92                  |

|        | 1k       | 3.94                  | 3.93                                                               | 3.93                  | 3.93                  |

|        | 10k      | 3.95                  | 3.95                                                               | 3.94                  | 3.95                  |

| -      | 10       | 3.91                  | 3.90                                                               | 3.89                  | 3.90                  |

|        | 100      | 3.90                  | 3.90                                                               | 3.89                  | 3.90                  |

|        | 1k       | 3.91                  | 3.91                                                               | 3.91                  | 3.91                  |

|        | 10k      | 3.93                  | 3.92                                                               | 3.92                  | 3.92                  |

Table 4 Individual IC's Supply Current Dependence on Chip Location

| inpu  | Loci      | tion( | 41 | 1  |     | 4  | 2   |    | 3   | 4  | 1   | ] ] |    | 1  | 2   | 0  | )   | 4  | 1  | 1  | L   | 2  | 2  | :  | 3   | (  | D   | 1  | L   | 0 | D  | Ι | 4  | )   | 1  | 1 |

|-------|-----------|-------|----|----|-----|----|-----|----|-----|----|-----|-----|----|----|-----|----|-----|----|----|----|-----|----|----|----|-----|----|-----|----|-----|---|----|---|----|-----|----|---|

|       | ( = 1 K   | 0.    | 2  | 0. | 91  | 0. | 9 3 | 0. | 9 5 | 0. | 95  | 0.  | 90 | 0. | 95  | 18 | . 1 | 0. | 94 | 0. | 9 3 | 0. | 94 | 0. | 98  | 0. | 6 0 | 0. | 9 2 | 1 | 8. | 7 | 0. | 6 2 | 0. | 4 |

| +     | (11z)     | 10.   | 0  | 0. | 83  | 0. | 9 2 | 0. | 9 5 | 0. |     | 0.  | 91 | 0. | 96  | 18 | . 1 | 0. | 94 | 0. | 94  | 0. | 93 | 0. | 96  | 0. | 7 3 | 0. | 9 6 | 1 | 8. | 5 | 0. | 6 2 | 0. | 4 |

| Ċ j   | f = 1 0 K | 0.    | 2  | 0. | 9 2 | 0. | 9 2 | 0. | 9 5 | 0. | 9 5 | 0.  | 91 | 0. | 95  | 18 | . 1 | 0. | 94 | 0. | 93  | 0. | 94 | 0. | .96 | 0. | 6 0 | 0. | 9 2 | 1 | 8. | 5 | 0. | 6 2 | 0. | 4 |

| 11    | (Hz)      | 10.   | 0  | 0. | 9 5 | 0. | 9 2 | 0. | 96  | 0. | 95  | 0.  | 94 | 0. | 95  | 18 | . 1 | 0. | 94 | 0. | 95  | 0. | 94 | 0. | 96  | 0. | 6 0 | 0. | 9 5 | 1 | 8. | 5 | 0. | 6 2 | 0. | 4 |

|       | 1 = 1 K   | 0.    | 2  | 0. | 91  | 0. | 9 0 | 0. | 95  | 0. | 9 5 | 0.  | 94 | 0. | 9 2 | 18 | . 2 | 0. | 98 | 0. | 93  | 0. | 91 | 0. | 95  | 0. | 6 3 | 0, | 9 2 | 1 | 8. | 5 | 0. | 6 1 | 0. | 4 |

| _     | (Hz)      | 10.   | 0  | 0. | 93  | 0. | 91  | 0. | 95  | 0. | 98  | 0.  | 95 | 0. | 94  | 18 | . 2 | 0. | 98 | 0. | 94  | 0. | 91 | 0. | 96  | 0. | 73  | 0. | 9 6 | 1 | 8. | 2 | 0. | 6 1 | 0. | 4 |

|       | f = 1 0 K | 0.    | 2  | 0. | 92  | 0. | 9 0 | 0. | 95  | 0. | 98  | 0.  | 95 | 0. | 9 2 | 18 | . 2 | 0. | 98 | 0. | 93  | 0. | 91 | 0. | 95  | 0. | 6 3 | 0. | 9 2 | 1 | 8. | 1 | 0. | 6 1 | 0. | 4 |

| 1 - ( | (Hz)      | 10.   | 0  | 0. | 95  | 0. | 91  | 0. | 9 5 | 0. | 98  | 0.  | 96 | 0. | 9 2 | 18 | . 1 | 0. | 98 | 0. | 9 5 | 0. | 91 | 0. | 95  | 0. | 6 3 | 0. | 94  | 1 | 8. | 1 | 0. | 6 1 | 0. | 4 |

(1,2,3) and 4) in the filter circuit, and performing the fault experiment, a 100% fault detection rate was obtained.

1

Defective IC-Op Amps

[Positive supply current] ①18.10 [mA] ② 0.47 [mA] ③50.60 [mA] ④ 0.60 [mA]

The above values were taken when the IC-Op Amp was configured as a voltage follower.

\* Computed Versus Measured Value <Non Fault>

| s.<br>Lette heater               | 10 |   | <ul><li>Computed</li><li>Measured</li></ul>                                        | Value          | 3.92  | [mA]         |

|----------------------------------|----|---|------------------------------------------------------------------------------------|----------------|-------|--------------|

| and the second                   |    | - | <ul> <li>Computed</li> <li>Measured</li> </ul>                                     | Value          | 3.76  | [mA]         |

| pané NJ<br>Laga Két<br>Jangé apa |    | _ | <ul> <li>Computed</li> <li>Measured</li> <li>Computed</li> <li>Measured</li> </ul> | Value<br>Value | 0.018 | [mA]<br>[mA] |

<Insertion of Defective IC-Op Amp to A3 Case>

µ: + · Computed Value 0.94 × 4 + 18.1

= 21.86 [mA]

· Measured Value 21.70 [mA]

- · Computed Value 0.94 × 4 + 18.1 = 21.86 [mA] · Measured Value 21.50 [mA]

This falls under the Fault Model Case 5 since the non fault IC-Op Amp supply current is constant. Also, in this case the computed value is equal to measured value.

But when defective IC and is inserted to the IC-Op Amp A2 and A3 position, the supply current of IC-Op Amp A4 increases. Thus, the IC and A4 combination falls under the Fault Model Case 4.

Since the same IC-Op Amp ( $\mu$ A741) was used in all the 3 circuits, thus, the value of  $\sigma$  is smaller than the computed value for all the three circuits.

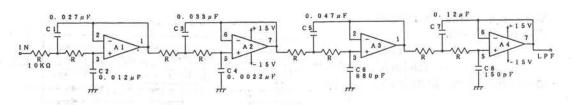

#### 7. Supply Current Test Limit

Increasing the number of ICs on the board inevitably increases the supply current thus, widening the threshold level.

Consequently, even if the IC is defective, and the variation in the supply current falls within the threshold range, it is not possible to detect the fault.

Hence, this paper theoretically discusses the limits in the supply current fault detection method.

Assumme that the IC-Op Amp's supply current is a normal distribution. When n is the number of IC-Op Amps on the PCB, M is the mean of the total board supply current and s the standard deviation. When each IC-Op Amp's mean is  $\mu_i$  and standard deviation  $\sigma_i$  (i=1,2,..n), by statistical theory:

$$M = \sum_{i=1}^{n} \mu_i \tag{9}$$

$$\sigma = \sqrt{\sum_{i=1}^{n} \sigma_i^2} \tag{10}$$

Assuming that the IC-Op Amps are all of the same type, equation (9) and (10) becomes

$$M = n \mu \tag{11}$$

$$s = \sqrt{n} \sigma \tag{12}$$

For the non fault ICs, the supply current threshold range is:

$$M \pm 3 s$$

(13)

Using equation (12) and (13),

$$3s = 3\sqrt{n}\sigma \tag{14}$$

When the supply current is larger than 3s of equation (14), it is possible to detect faults.

Assume  $I_F$  to be the total supply current. When one of the n Op Amps is at the fault condition, with  $I_F$  increasing or decreasing in value, and falls within the 3s range, it is not possible to detect the fault. Thus, the limit of fault detection becomes

$$3\sqrt{n}\,\sigma = I_{\rm F} \tag{15}$$

Using equation (12), with  $\sigma$  (=0.2) and  $\mu$  (=I<sub>F</sub>=2.07) of the piecewise linear circuit, n is calculated to be 11 ICs. This result means that if the number of ICs is more than 11, it is not possible to detect the fault.

As shown in chapter 3, the measured value of

$\sigma$  is smaller than the computed value by about 70%. Using this fact to calculate n, the value of n = 36 chips is obtained.

If the number of ICs is more than 11, equation (15) becomes

$$3\sqrt{n} \sigma > I_F$$

(16)

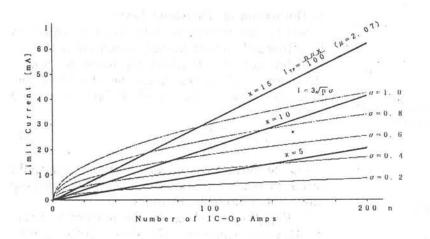

The n and I<sub>F</sub> relationship with varying values of the  $\sigma$  parameter is shown in Fig. 9. This figure shows that the threshold range increases as the number of ICs n increases, making it difficult to detect faults.

### 8. Discussion of Threshold Level

Setting the threshold level mean  $\mu$  equal to  $I_{TP}$  (standard current value), assuming a threshold level of  $\pm x\%$  about the mean  $\mu$ , and n the number of IC-Op Amps on the PCB, the absolute value of the threshold level  $\mu x \swarrow 100$  becomes,

$$I_{\rm TP} = \frac{n\mu x}{100} \tag{17}$$

Fig. 10 shows the comparison of the threshold levels in equation (15) and (17) with varying values of parameter  $\sigma$  and x.

In Fig. 12, depending on the parameter value x, the linear equation (17) gives a better threshold value I for small values of n, while the non linear equation (15) gives the better threshold value for large values of n.

Calculating for the percent value of  $3\sigma$  to the  $\mu$  value

$$\frac{3\sigma}{\mu} \times 100 \% \tag{18}$$

As an example, applying the values from the piecewise linear circuit with  $\sigma = 0.2$ , and  $\mu = 17.1$  gives a result of 3.5%.

Using the  $3\sigma$  value is better than the fixed threshold value (percent value) because the  $3\sigma$ value can vary depending on a random variable which is the IC supply current.

#### 9. Conclusion

By experiment the IC-Op Amp's supply current represented a random variable with normal distribution whose threshold value was determined to be  $\mu \pm 3\sigma$ . Inserting a defective Op Amp into the discrete circuit, the fault experiment obtained an 81% fault detection

Fig.9 n and I<sub>F</sub> Relationship with the  $\sigma$  Parameter

Fig.10 Threshold Level Comparison

rate.

This paper introduced a model to represent the IC-Op Amp in the analog circuit. The results were obtained by applying this model to 3 circ uits using the  $\mu A$  741.

When the threshold level of one IC was used in the same way to determine the threshold level of each of the 3 boards, a fault detection rate of approximately 90% was obtained for the above mentioned 3 circuits.

This paper discussed the limit of fault detection, assuming that one IC's mean supply current increased or decreased when a fault occurred at the IC-Op Amp in the PCB.

The results of this research, verified the usefulness of the supply current test to detect faults in analog circuits.

However, the applicability of the supply current test to detect fault ICs in other circuits aside from those tested in this paper should be verified. The next step in the research process would be to diagnose fault ICs using the supply current test if applicable or by using another method.

#### References

- K.D. Wangner and T.W. Williams, "Design for Testability of Mixed Signal Integrated Circuits", Proc. Int. Test Conf., pp.823-828 1988.

- [2] M.J. Mrlett and J.A. Abraham. "DC\_IA TP-An Iterative Analog Circuit Test Generation Program for Generating DC Single Pattern Tests", Proc. Int. Test Conf., pp.839-844, 1988.

- [3] A. Meixner and W. Maly, "Fault Modeling for the Testing of Mixed Integrated Circuits", Proc. Int. Test Conf., pp.564-572, 1991. (Received Sept. 30, 1997)